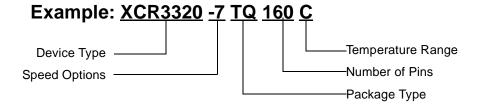

# XCR3320: 320 Macrocell SRAM CPLD

DS033 (v1.3) October 9, 2000

## **Product Specification**

### **Features**

- 320 macrocell SRAM based CPLD

- · Configuration times of under 1.0 second

- IEEE 1149.1 compliant JTAG testing capability

- Five pin JTAG interface

- IEEE 1149.1 TAP controller

- In system configurable

- 3.3V device with 5V tolerant I/O

- Innovative XPLA2 Architecture combines extreme flexibility and high speeds

- Eight synchronous clock networks with programmable polarity at every macrocell

- Up to 32 asynchronous clocks support complex clocking needs

- Innovative XOR structure at every macrocell provides excellent logic reduction capability

- Logic expandable to 36 product terms on a single macrocell

- Advanced 0.35

µ SRAM process

- Design entry and verification using industry standard and Xilinx CAE tools

- Control Term structure provides either sum terms or product terms in each logic block for:

- 3-state buffer control

- Asynchronous macrocell register reset/preset

- Global 3-state pin facilitates "bed of nails" testing without sacrificing logic resources

- Programmable slew rate control

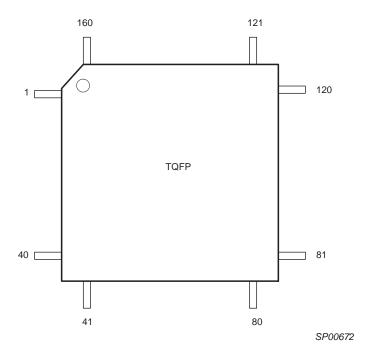

- Small form factor packages with high I/O counts

- Available in commercial and industrial temperature ranges

# **Description**

The XCR3320 device is a member of the CoolRunner<sup>®</sup> family of high-density SRAM-based CPLDs (Complex Programmable Logic Device) from Xilinx. This device combines high speed and deterministic pin-to-pin timing with high density. The XCR3320 uses the patented Fast Zero Power (FZP<sup>TM</sup>) design technique that combines high speed and low power for the first time ever in a CPLD. FZP allows the XCR3320 to have true pin-to-pin timing delays of 7.5 ns, and standby currents of 100 μA without the need for 'turbo bits' or other power down schemes. By replacing conventional sense amplifier methods for implementing product terms (a technique that has been used since the bipolar era) with a cascaded chain of pure CMOS gates, both standby and dynamic power are dramatically reduced when compared to other CPLDs. The FZP design tech-

nique is also what allows Xilinx to offer a true CPLD architecture in a high density device.

The Xilinx XCR3320 devices use the patented XPLA2 (eXtended Programmable Logic Array) architecture. This architecture combines the best features of both PAL- and PLA-type logic structures to deliver high speed and flexible logic allocation that results in superior ability to make design changes with fixed pinouts. The XPLA2 architecture is constructed from 80 macrocell Fast Modules that are connected together by an interconnect array. Within each Fast Module are four Logic Blocks of 20 macrocells each. Each Logic Block contains a PAL structure with four dedicated product terms for each macrocell. In addition, each Logic Block has 32 additional product terms in a PLA structure that can be shared through a fully programmable OR array to any of the 20 macrocells. This combination efficiently allocates logic throughout the Logic Block, which increases device density and allows for design changes without re-defining the pinout or changing the system timing. The XCR3320 offers pin-to-pin propagation delays of 7.5 ns through the PAL array of a Fast Module; and if the PLA array is used, an additional 1.5 ns is added to the delay, no matter how many PLA product terms are used. If the interconnect array between Fast Modules is used, there is a second fixed delay of 2.0 ns. This means that the worst case pin-to-pin propagation delay within a fast module is 7.5 + 1.5 = 9.0 ns, and the delay from any pin to any other pin across the entire chip is 7.5 + 2.0 = 9.5 ns if only the PAL array is used, and 7.5 + 1.5 + 2.0 = 11.0 ns if the PLA array is used.

Each macrocell also has a two input XOR gate with the dedicated PAL product terms on one input and the PLA product terms on the other input. This patent-pending Versatile XOR structure allows for very efficient logic optimization compared to competing XOR structures that have only one product term as the second input to the XOR gate. The Versatile XOR allows an 8-bit XOR function to be implemented in only 20 product terms, compared to 65 product terms for the traditional XOR approach.

The XCR3320 is SRAM-based, which means that it is configured from an external source at power up. See the configuration section of this data sheet for more information. The device supports the full JTAG specification (IEEE 1149.1) through an industry standard JTAG interface. It can also be configured through the JTAG port, which is very useful for prototyping. See section titled "Device Configuration Through JTAG" on page 29 for more information.

The XCR3320 CPLDs are supported by industry standard CAE tools (Cadence/OrCAD, Exemplar Logic, Mentor, Synopsys, Synario, Viewlogic, and Synplicity), using text (ABEL, VHDL, Verilog) and/or schematic entry. Design verification uses industry standard simulators for functional and timing simulation. Development is supported on personal computer, Sparc, and HP platforms. Device fitting uses a Xilinx developed tool including WebFITTER.

## XPLA2 Architecture

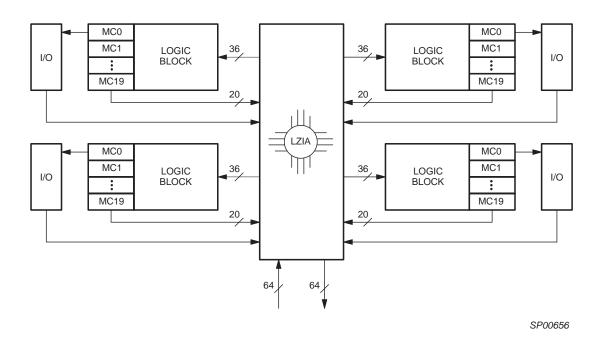

Figure 1 shows a high level block diagram of the XCR3320 implementing the XPLA2 architecture. The XPLA2 architecture is a multi-level, modular hierarchy that consists of Fast Modules interconnected by a virtual crosspoint switch

called the Global Zero Power Interconnect Array (GZIA). Each Fast Module accepts 64 bits from the GZIA and outputs 64 bits to the GZIA. Each Fast Module is essentially an 80 macrocell CPLD with four logic blocks of 20 macrocells each inside. There are eight dedicated, low-skew, global clocks for the device; and each Fast Module has access to any two of these clocks (there are additional asynchronous clocks available in the Fast Modules, see Figure 3. There are also Global 3-state (gts) and Global Reset (rstn) pins that are common to all Fast Modules. When gts is pulled high, all output buffers in the device will be disabled, causing all I/O pins to be tri-stated. When rstn is pulled low, all flip-flops of the device will be reset.

Figure 1: Xilinx XPLA2 CPLD Architecture

#### XPLA2 Fast Module

Each Fast Module consists of four Logic Blocks of 20 macrocells each. Depending on the package, either seven or 12 of the 20 macrocells in each Logic Block are connected to I/O pins, and the remaining macrocells are used as buried nodes. These four Logic Blocks are connected together by the Local Zero Power Interconnect Array (LZIA). The

LZIA is a virtual crosspoint switch that connects the Logic Blocks to each other and to the GZIA. The feedback from all 80 macrocells, input from the I/O pins, and the 64 bit input bus from the GZIA are input into the LZIA. The LZIA outputs 36 signals into each Logic Block and 64 signals into the GZIA (Figure 2).

Figure 2: Xilinx XPLA2 Fast Module

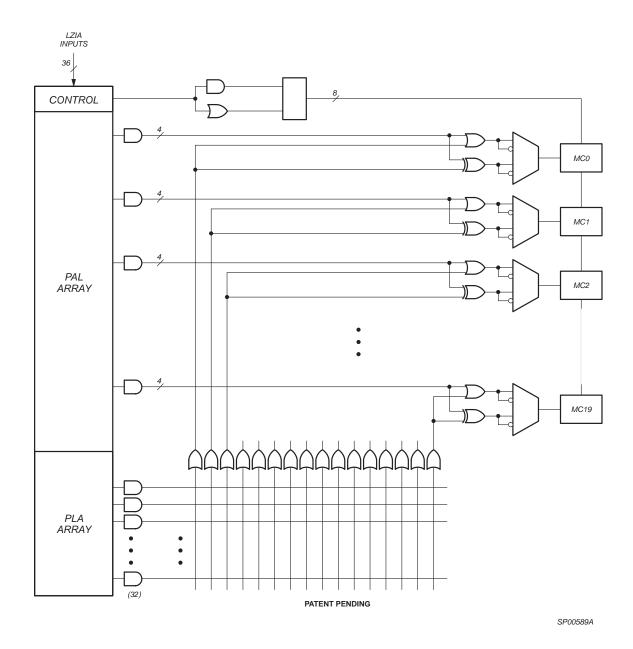

## XPLA2 Logic Block Architecture

Figure 3 illustrates the XPLA2 Logic Block architecture. Each Logic Block contains eight control terms, a PAL array, a PLA array, and 20 macrocells. The 36 inputs from the LZIA are available to all control terms and to each product term in both the PAL and the PLA array. The eight control terms can individually be configured as either SUM or PRODUCT terms, and are used to control the asynchronous preset and reset functions of the macrocell registers, the output enables of the 20 macrocells, and for asynchronous clocking. The PAL array consists of a programmable AND array with a fixed OR array, while the PLA array con-

sists of a programmable AND array with a programmable OR array.

Each macrocell has four dedicated product terms from the PAL array. When additional logic is required, each macrocell takes the extra product terms from the PLA array. The PLA array consists of 32 extra product terms that are shared between the 20 macrocells of the Logic Block. The PAL product terms can be connected to the PLA product terms through either an OR gate or an XOR gate. One input to the XOR gate can be connected to all the PLA terms, which provides for extremely efficient logic synthesis. An eight bit XOR function can be implemented in only 20 product terms. Each macrocell can use the output from the OR gate or the XOR gate in either normal or inverted state.

Figure 3: Xilinx XPLA2 Logic Block Architecture

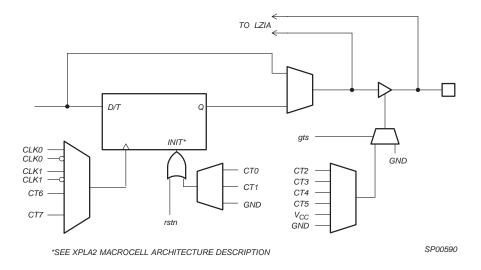

## **XPLA2 Macrocell Architecture**

Figure 4 shows the XPLA2 macrocell architecture used in the XCR3320. The macrocell can be configured as either a D- or T-type flip-flop or a combinatorial logic function. A D-type flip-flop is generally more useful for implementing state machines and data buffering while a T-type flip-flop is generally more useful in implementing counters. Each of these flip-flops can be clocked from any one of four sources. Two of the clock sources (CLK0 and CLK1) are from the eight dedicated, low-skew, global clock networks designed to preserve the integrity of the clock signal by reducing skew between rising and falling edges. These clocks are designated as "synchronous" clocks and must be driven by an external source. Both CLK0 and CLK1 can clock the macrocell flip-flops on either the rising edge or the falling edge of the clock signal. The other clock sources are designated as "asynchronous" and are connected to two of the eight control terms (CT6 and CT7) provided in each logic block. These clocks can be individually configured as any PRODUCT term or SUM term equation created from the 36 signals available inside the logic block. Thus, in each Logic Block, there are up to four possible clocks; and in each Fast Module, there are up to ten possible clocks. Throughout the entire device, there are up to 40 possible clocks-eight from the dedicated, low-skew, global clocks, and two for each of the 16 logic blocks.

The remaining six control terms of each logic block (CT0-CT5) are used to control the asynchronous preset/reset of the flip-flops and the enable/disable of the output buffers in each macrocell. Control terms CT0 and CT1 are used to control the asynchronous preset/reset of the macrocell's flip-flop. Note that the power-on reset leaves all macrocells in the "zero" state when power is properly

applied, and that the preset/reset feature for each macrocell can also be disabled. Each macrocell can choose between an asynchronous reset or an asynchronous preset function, but both cannot be simultaneously used on the same register. The global rstn function can always be used, regardless of whether or not asynchronous reset or preset control terms are enabled. Control terms CT2, CT3, CT4 and CT5 are used to enable or disable the macrocell's output buffer. The output buffers can also be always enabled or always disabled. All CoolRunner devices also provide a Global 3-state (GTS) pin, which, when pulled high, will 3-state all the outputs of the device. This pin is provided to support "In-Circuit Testin" or "Bed-of-Nails" testing used during manufacturing.

For the macrocells in the Logic Block that are associated with I/O pins, there are two feedback paths to the LZIA: one from the macrocell, and one from the I/O pin. The LZIA feedback path before the output buffer is the macrocell feedback path, while the LZIA feedback path after the output buffer is the I/O pin feedback path. When these macrocells are used as outputs, the output buffer is enabled, and either feedback path can be used to feedback the logic implemented in the macrocell. When the I/O pins are used as inputs, the output buffer of these macrocells will be 3-stated and the input signal will be fed into the LZIA via the I/O feedback path. In this case the logic functions implemented in the buried macrocell can be fed back into the LZIA via the macrocell feedback path. For macrocells that are not associated with I/O pins, there is one feedback path to the LZIA. Logic functions implemented in these buried macrocells are fed back into the LZIA via this path. All unused inputs and I/O pins should be properly terminated. Please refer to "Terminations" on page 8.

Figure 4: XCR3320 Macrocell Architecture

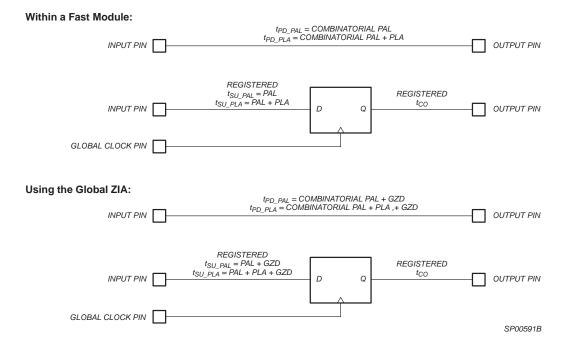

## **Simple Timing Model**

Figure 5 shows the XCR3320 timing model. The XCR3320 timing model is very simple compared to the models of competing architectures. There are three main timing parameters: the pin-to-pin delay for combinatorial logic functions ( $t_{PD}$ ), the input pin to register set up time ( $t_{SU}$ ), and the register clock to valid output time ( $t_{CO}$ ). As the model shows, timing is only dependent on whether or not the PLA array is used, and whether or not the logic function is created within a single Fast Module or uses the GZIA. The timing starts with a set time for  $t_{PD}$  and  $t_{SU}$  through the

PAL array in a Fast Module, and there are fixed delays added for use of the PLA array or the GZIA. The  $t_{CO}$  (pin-to-pin) timing specification never changes. For example, a combinatorial logic function of four or fewer product terms constructed from inputs within the same logic block would have a  $t_{PD}$  delay of 7.5 ns. If the logic function were more than four product terms wide, the delay would be  $t_{PD}$  plus the fixed PLA delay, or 7.5 +1.5 = 9.0 ns. A function that used the PAL array and inputs from a different Fast Module would have a propagation delay of  $t_{PD}$  plus the fixed GZIA delay, or 7.5 + 2.0 = 9.5 ns.

Figure 5: XCR3320 Timing Module

# **TotalCMOS Design Technique for Fast Zero Power**

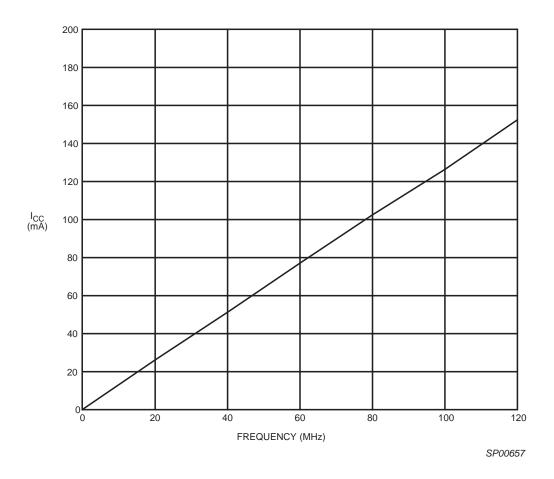

Xilinx is the first to offer a TotalCMOS CPLD, both in process technology and design technique. Xilinx employs a cascade of CMOS gates to implement its product terms instead of the traditional sense amp approach. This CMOS gate implementation allows Xilinx to offer CPLDs which are

both high performance and low power, breaking the paradigm that to have low power, you must have low performance. This also makes it possible to manufacture high density CPLDs like the XCR3320 that consume a fraction of the power of competing devices. Refer to Figure 6 and Table 1 showing the  $I_{CC}$  vs. Frequency of the XCR3320 TotalCMOS CPLD (data taken with 20 16-bit counters at 3.3V, 25°C, output buffers disabled).

Figure 6: I<sub>CC</sub> vs. Frequency at V<sub>CC</sub> = 3.3V, 25°C

Table 1:  $I_{CC}$  vs. Frequency ( $V_{CC} = 3.3V, 25^{\circ}C$ )

| Frequency (MHz)              | 0    | 1   | 20 | 40 | 60 | 80  | 100 | 120 |

|------------------------------|------|-----|----|----|----|-----|-----|-----|

| Typical I <sub>CC</sub> (mA) | 0.01 | 1.3 | 26 | 51 | 77 | 102 | 126 | 152 |

#### **Terminations**

The CoolRunner XCR3320 CPLDs are TotalCMOS™ devices. As with other CMOS devices, it is important to consider how to properly terminate unused inputs and I/O pins when fabricating a PC board. Allowing unused inputs and I/O pins to float can cause the voltage to be in the linear region of the CMOS input structures, which can increase the power consumption of the device. It can also cause the voltage on a configuration pin to float to an unwanted voltage level, interrupting device operation.

The XCR3320 CPLDs have programmable on-chip pull-down resistors on each I/O pin. These pull-downs are automatically activated by the fitter software for all unused I/O pins. Note that an I/O macrocell used as buried logic that does not have the I/O pin used for input is considered to be unused, and the pull-down resistors will be turned on. We recommend that any unused I/O pins on the XCR3320 device be left unconnected.

There are no on-chip pull-down structures associated with dedicated pins used for device configuration or special device functions like global reset and global 3-state. Xilinx recommends that these pins be terminated consistent with pin functionality. Xilinx recommends the use of weak pull-up and pull-down resistors for terminating these pins. See the appropriate configuration section for more information on terminating dedicated pins.

When using the JTAG Boundary Scan functions, it is recommended that  $10k\Omega$  pull-up resistors be used on the tdi, tms, tck, and trstn pins. The tdo signal pin can be left floating unless it is connected to the tdi of another device. Letting these signals float can cause the voltage on tms to

come close to ground, which could cause the device to enter JTAG/ISP mode at unspecified times.

# **Configuration Introduction**

The Xilinx CoolRunner series are available in technologies which use non-volatile (EEPROM-based) and volatile (SRAM based) configuration memory. The functionality of the XPLA2 family of the CoolRunner series is defined by on-chip SRAM. The devices are configured in a manner similar to that of most FPGAs. This section describes the configuration of the XCR3320, and applies to all similarly configured devices to be produced by Xilinx.

Either Xilinx or third party software is used to generate a JEDEC file. The JEDEC file contains the configuration data, which is loaded into the XCR3320 configuration memory to control the XCR3320 functionality. This is done at power-up and/or with configure command. This section provides some of the trade-offs in selecting a configuration mode, and provides debug hints for configuration problems.

There are several different methods of configuring the XCR3320. The mode used is selected using the mode select pins. There are three basic configuration methods: master, slave, and peripheral. The configuration data can be transmitted to the XCR3320 serially or in parallel bytes. As a master, the XCR3320 generates the clock and control signals to strobe configuration data into the XCR3320. As a slave device, a clock is generated externally, and provided into the XCR3320 sclk pin. In the peripheral mode, the XCR3320 interfaces as a microprocessor peripheral. Please note that M3 should always be High. Table 2 lists the states for the other mode pins by configuration mode.

**Table 2: Configuration Modes**

| M2 | M1 | MO | Cclk   | Configuration Mode     | Data Format |  |  |

|----|----|----|--------|------------------------|-------------|--|--|

| 0  | 0  | 0  | Output | Master serial          | Serial      |  |  |

| 0  | 0  | 1  | Input  | Slave parallel         | Parallel    |  |  |

| 0  | 1  | 0  |        | Reserved               |             |  |  |

| 0  | 1  | 1  | Input  | Synchronous peripheral | Parallel    |  |  |

| 1  | 0  | 0  | Output | Master parallel - up   | Parallel    |  |  |

| 1  | 0  | 1  |        | Reserved               |             |  |  |

| 1  | 1  | 0  |        | Reserved               |             |  |  |

| 1  | 1  | 1  | Input  | Slave serial           | Serial      |  |  |

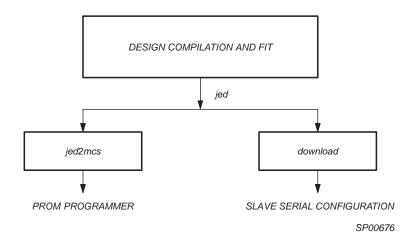

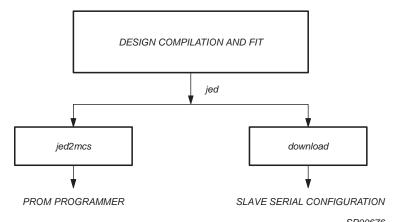

## **Design Flow Overview**

Figure 7 is a diagram of the steps used in configuring the XCR3320. The development system is used to generate configuration data in the JEDEC file. Using the <design>.jed file, there are two general methods of configuring the XCR3320. The utility download can load the

configuration data from a PC or workstation hard disk into the XCR3320. Alternately, the XCR3320 can be loaded from non-volatile ICs such as serial or parallel EEPROMs, after converting the JEDEC file to an MCS file using the <code>jed2mcs</code> utility.

Figure 7: Design Flow

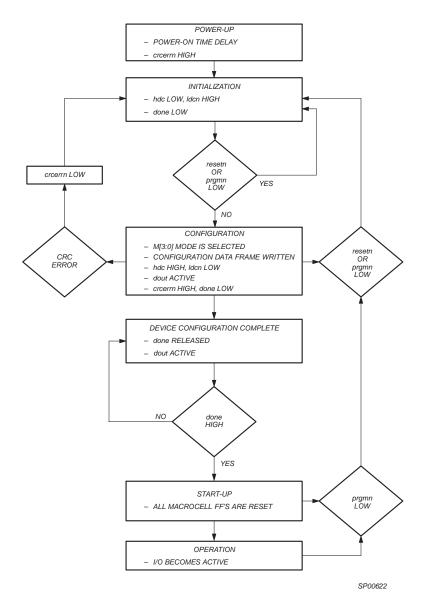

# **XCR3320 States Of Operation**

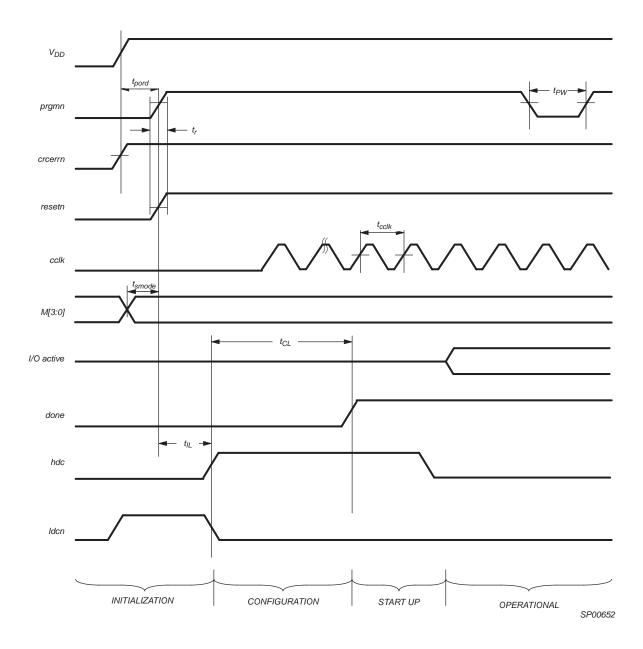

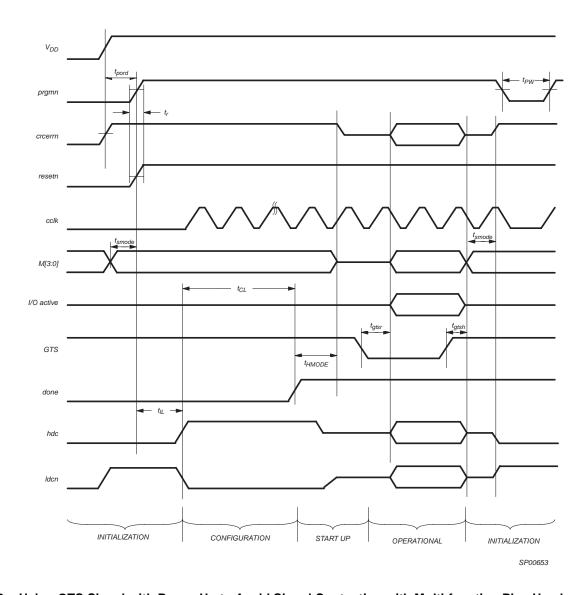

Prior to becoming operational, the XCR3320 goes through a sequence of states, including initialization, configuration, and start-up. This section discusses these three states. In the master configuration modes, the XCR3320 is the source of configuration clock (cclk).

When configuration is initiated, a counter in the XCR3320 is set to zero and begins to count configuration clock cycles applied to the XCR3320. As each configuration data frame is supplied to the XCR3320, it is internally assembled into data words. Each data word is loaded into the internal configuration memory. The configuration loading process is

complete when the internal length count equals the loaded length count in the length count field, and the required end of configuration frame is written.

All configuration I/Os used as inputs operate with TTL-level input thresholds during configuration. All I/Os that are not used during the configuration process are 3-stated with internal pull-downs. During configuration, registers are reset. The combinatorial logic begins to function as the XCR3320 is configured. Figure 6 shows the flow between the initialization, configuration, and start-up states. Figure 9 gives the general timing information for configuring the device.

Figure 8: Chart Of Initialization, Configuration, and Operating States

Figure 9: General Configuration Mode Timing Diagram

**Table 3: General Configuration Mode Timing Characteristics**

| Symbol             | Parameter                                               |               |      | Max. | Unit |

|--------------------|---------------------------------------------------------|---------------|------|------|------|

| All Configu        | ration Modes                                            |               |      |      |      |

| t <sub>SMODE</sub> | M[3:0] setup time to prgmn high                         |               | 0    | -    | ns   |

| t <sub>HMODE</sub> | M[3:0] hold time from done high                         |               | 10   | -    | ms   |

| t <sub>PW</sub>    | prgmn pulse width low                                   |               | 50   | -    | ns   |

| t <sub>gtsr</sub>  | Global 3-state disable                                  |               |      | 40   | ns   |

| t <sub>IL</sub>    | Initialization latency (prgmn high to hdc high) XCR3320 | M3 = 1        | 250  | 700  | ns   |

| t <sub>PORD</sub>  | Power-on reset delay                                    | 1             |      | ms   |      |

| t <sub>r</sub>     | Configuration signal rise time                          |               |      | 1.0  | ms   |

| Master Mod         | les                                                     |               |      |      |      |

| t <sub>CCLK</sub>  | cclk period                                             | M3 = 1        | 714  | 1667 | ns   |

| t <sub>CL</sub>    | Configuration latency (non-compressed) M3 = 1 XCR3320   |               | 135  | 316  | ms   |

| Slave Serial       | , Slave Parallel, And Synchronous Peripheral Mod        | es            |      |      |      |

| t <sub>CCLK</sub>  | cclk period                                             | Single device | 100  | -    | ns   |

|                    |                                                         | Daisy-chain   | 1000 | -    | ns   |

| t <sub>CL</sub>    | Configuration latency (non-compressed)                  | Single device | 19   | -    | ms   |

|                    | XCR3320                                                 | Daisy-chain   | 189  | -    | ms   |

|                    | •                                                       |               |      | •    |      |

#### Initialization

Upon power-up, the device goes through an initialization process. First, an internal power-on-reset circuit is triggered when power is applied. When V<sub>CC</sub> reaches the voltage at which portions of the XCR3320 begin to operate (1.5V), the configuration pins are set to be inputs or outputs based on the configuration mode, as determined by the mode select inputs M[2:0]. The mode pins must be stable t<sub>SMODE</sub> nanoseconds before the rising edge of prgmn or resetn. A time-out delay is initiated when V<sub>CC</sub> reaches between 1.0V and 2.0V to allow the power supply voltage to stabilize. The done output is low. At power-up, if the power supply does not rise from 1.0V to V<sub>CC</sub> in less than 25 ms, the user should delay configuration by inputting a low into prgmn or resetn until V<sub>CC</sub> is greater than the recommended minimum operating voltage (3.0V for commercial devices). If prgmn has a rise time of greater than one microsecond, resetn must be held low until after promin goes high. If the rise time for prgmn is 1 ms or less, the order in which these pins go high is arbitrary.

The High During Configuration (hdc), Low During Configuration (ldcn), and done signals are active outputs in the XCR3320's initialization and configuration states. hdc, ldcn, and done can be used to provide control of external logic signals such as reset, bus enable, or EEPROM enable during configuration. For master parallel configuration mode, these signals provide EEPROM enable control and allow the data pins to be shared with user logic signals.

If configuration has begun, an assertion of resetn or prgmn initiates an abort, returning the XCR3320 to the initializa-

tion state. The resetn and prgmn pins must be high before the XCR3320 will enter the configuration state, and the mode pins must be stable  $t_{\text{SMODE}}$  nanoseconds before they rise. During the start-up and operating states, only the assertion of prgmn causes a reconfiguration.

During initialization and configuration, all I/O's are 3-stated and the internal weak pull-downs are active. See "Terminations" on page 8 for more information.

#### Start-up

After configuration, the XCR3320 enters the start-up phase. This phase is the transition between the configuration and operational states. This transition occurs within three cclk cycles of the done pin going high (it is acceptable to have additional cclk cycles beyond the three required). The system design task in the start-up phase is to ensure that multi-function pins (See "230-pin Function Table" on page 36.) transition from configuration signals to user definable I/Os without inadvertently activating devices in the system or causing bus contention. The done signal goes High at the beginning of the start up phase, which allows configuration sources to be disconnected so that there is no bus contention when the I/Os become active. In addition to controlling the XCR3320 during start-up, additional start-up techniques to avoid contention include using isolation devices between the XCR3320 and other circuits in the system, re-assigning I/O locations, and keeping I/Os 3-stated until contentions are resolved. For example, Figure 10 shows how to use the Global 3-state (GTS) signal to avoid signal contention when any multi-function pins

Figure 10: Using GTS Signal with Power Up to Avoid Signal Contention with Multi-function Pins Used as I/O

are used as I/O after configuration is finished. Holding gts high until after the multi-function pins are disconnected from the driving source allows these pins to transition from configuration pins to user definable I/O without signal contention. In this case, the I/O become active a  $t_{\rm GTSR}$  delay after the gts pin is pulled low.

The flip-flops are reset one cycle after done goes high so that operation begins in a known state. The done outputs from multiple XCR3320s can be wire ANDed and used as an active-high ready signal, to disable PROMs with active-low enable(s), or to reset to other parts of the system (see Figure 27).

# **Configuration Data Format Overview**

The XCR3320 functionality is determined by the state of internal configuration RAM. This section discusses the configuration data format, and the function of each field in configuration data packets.

## **Configuration Data Packets**

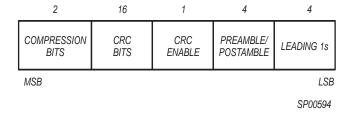

Configuration of the XCR3320 is done using configuration packets. The configuration packet is shown in Figure 11. The data packet consists of a header and a data frame. There are four types of data frames. The header is shifted into the device first, followed by one data frame. Configuration of a single XCR3320 requires 338 data packets, one for each address. All preceding data must contain only 1's. Once a device is configured, it retransmits data of any polarity. Before and during configuration, all data retransmitted out the daisy-chain port (dout) are 1's.

|     |            | 27     | 27     |    |

|-----|------------|--------|--------|----|

|     | DATA FRAME | HEADER | HEADER | ]  |

| MSB |            |        | LS     | В  |

|     |            | SP00   | SP0059 | 93 |

Figure 11: Data Packet

The ordering of the data packets may be random, but they cannot be mixed with other devices' data packets. Alignment bits are not required between data packets. If used, alignment bits must be included in the length count, and they must be at least 2-bits long.

**Table 4: Configuration Frame Size**

| Device                                               | XCR3320 |

|------------------------------------------------------|---------|

| Number of frames                                     | 338     |

| Data bits/standard frame                             | 560     |

| Data bits/compressed frame                           | 14      |

| Data bits/user_code frame                            | 560     |

| Data bits/isc_code frame                             | 560     |

| Maximum configuration data – # bits/frame x # frames | 189280  |

Figure 12: 27-bit Header

The header is fixed and consists of five fields:

- Leading 1s,

- · Preamble,

- · CRC Enable,

- · CRC Bits,

- Compression Bits.

The leading 1s enter the device first. The following is a description of each field in the header.

#### Leading 1s:

This is a four or greater bit field consisting of 1s.

#### Preamble/Postamble:

This is a four bit field which indicates the start of a frame or the end of configuration:

Preamble: -0010 - signals the beginning of a configuration data packet.

Postamble: 0100 -signals the end of configuration. All other values of the preamble field force configuration of the entire system to restart.

The segments CRC Enable, CRC Bits, and Compression Bits are valid only if the Preamble field is 0010.

#### Cyclic Redundancy Check (CRC) Enable:

In this single bit field, a 0 disables CRC checking of the data stream. If the CRC is disabled the 16 bit CRC field must be the default described below. A1 enables CRC error checking of the data stream.

#### **CRC Error Checking:**

The CRC field is a 16 bit field. The default value is 1010\_1010\_1010\_1010. The calculated value is from data, address, stop bit, and first alignment bit (starting with crc\_reg[15:0] = [0]). Using verilog operators, the crc is calculated as:

```

crc_reg[14:2] <= cr_reg[14:2] << 1;

cr_reg[2] <= cr_reg[15]^din^cr_reg[1];

cr_reg[1] <= cr_reg[0];

cr_reg[0] < cr_reg[15]^din;

cr_reg[15] <= cr_reg[15]^din^cr_reg[14];

If a CRC error is detected, configuration is halted and must be restarted.</pre>

```

#### Compression Bits:

This 2-bit field defines the use of compression of the data packets.

00 - Standard mode:

The data packet contains both address and data

01 - Reset mode:

The data packet contains only the address field. This pattern causes the configuration register to be reset.

10 - Hold mode:

The data packet contains only the address field. This pattern causes the configuration register to hold its value.

11 - Set mode:

The data packet contains only the address field. This pattern causes the configuration register to be set.

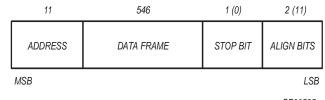

#### **Data Frames**

The four types of data frames are standard, compressed, user\_code, and isc\_code. All fields must be completely filled, with 1s used to fill unused bits. The definition of each frame is described below:

#### Standard Frame

SP00595

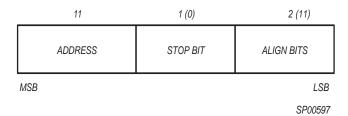

igure 13: Standard Frame

#### Address:

This is an 11 bit field for providing 338 (336 SRAM plus 2user) addresses.

#### Data:

546 bit field.

#### Stop bit:

This is a one bit field which must be 0.

## Align bit:

This is a two bit field which must be 11.

#### Compressed Frame

igure 14: Compressed Frame

The compressed frame contains no data.

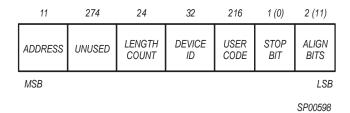

#### User Code Frame

Figure 15: User Code Frame

The user code is located at address 336.

## **Length Count:**

This is a 24 bit field containing the length of the data stream transmitted to configure all of the devices in the daisy chain. This field is only used by a XCR3320 if it is in the master mode.

#### **Device ID:**

This is a 32-bit field containing XCR3320 device ID: 0000\_001\_001\_010000\_1\_000\_0000010101\_1

#### **User Code:**

This is a 216 bit field reserved for user information.

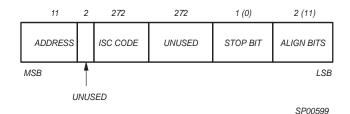

#### ISC Code Frame

The isc\_code address is 337.

Figure 16: ISC Frame

The ISC frame allows the user to write an ISC code to the device.

## Reconfiguration

To reconfigure the XCR3320 when the device is operating in the system, a low pulse is input into prgmn. The I/Os not used for configuration are 3-stated. The XCR3320 then samples the mode select inputs and begins re-configuration. The mode pins are continuously sampled, so the signals must be stable while prgmn is low. When configuration is compete, done is released, allowing it to be pulled high.

## **CRC Error Checking**

CRC checking is done on each frame if enabled by setting the CRCen bit in the header. If there is an error, a CRC error is flagged by pulling crcerrn low. The XCR3320 is forced into the initialization state, and then moves into the configuration state after prgmn and resetn go high. The XCR3320 will also pull crcerrn low if an invalid preamble is detected within a configuration data packet.

# **XCR3320 Configuration Modes**

The method for configuring the XCR3320 is selected by the m0, m1, and m2 inputs. The m3 input should be high for all modes. In master modes, cclk is an output with a nominal frequency of 1 MHz. In slave modes, cclk is an input with a maximum frequency of 10 MHz if configuring only a single device, and 1 MHz if devices are daisy chained.

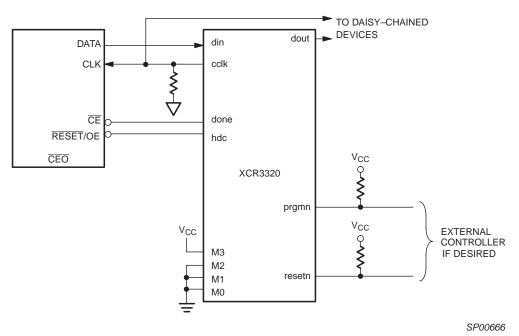

#### **Master Serial Mode**

In the master serial mode, the XCR3320 loads the configuration data from an external serial ROM. The configuration data is either loaded automatically at start-up or on a command to reconfigure. Serial EEPROMs from Altera, Atmel, Lucent, Microchip, and Xilinx can be used to configure the XCR3320 in the master serial mode. This provides a simple four-pin interface in an eight-pin package. Serial EEPROMs are available in 32K, 64K, 128K, 256K, and 1M bit densities.

Configuration in the master serial mode can be done at power-up and/or upon a configure command. The system or the XCR3320 must activate the serial EEPROM's RESET/OE and CE inputs. At power-up, the XCR3320 and serial EEPROM each contain internal power-on reset circuitry which allows the XCR3320 to be configured without the system providing an external signal. The power-on reset circuitry causes the serial EEPROMs' internal address pointer to be reset. After power-up, the XCR3320 automatically enters its initialization phase.

The serial EEPROM/XCR3320 interface used depends on such factors as the availability of a system reset pulse, availability of an intelligent host to generate a configure

command, whether a single serial EEPROM is used or multiple serial ROMs are cascaded, whether the serial EEPROM contains a single or multiple configuration programs, etc.

Data is read into the XCR3320 sequentially from the serial ROM. The DATA output from the serial EEPROM is connected directly into the din input of the XCR3320. The cclk output from the XCR3320 is connected to the CLOCK input of the serial EEPROM. During the configuration process, cclk clocks one data bit into the XCR3320 on each rising edge.

Since the data and clock are direct connects, the XCR3320/serial EEPROM interface task is to use the system or XCR3320 to enable the  $\overline{\text{RESET}}/\text{OE}$  and  $\overline{\text{CE}}$  of the serial EEPROM(s). The serial  $\overline{\text{EEPROM}}$ 's  $\overline{\text{RESET}}/\text{OE}$  is programmable to function with  $\overline{\text{RESET}}$  active-low and  $\overline{\text{OE}}$  active-high, which allows hdc from the XCR3320 to control this function.

Likewise, the serial EEPROM could be programmed to function with RESET active high and  $\overline{\text{OE}}$  active low, allowing the ldcn pin from the XCR3320 to control this function. The XCR3320 done pin is connected to the serial EEPROM  $\overline{\text{CE}}$  to enable the EEPROMs during configuration and disable them when configuration is complete.

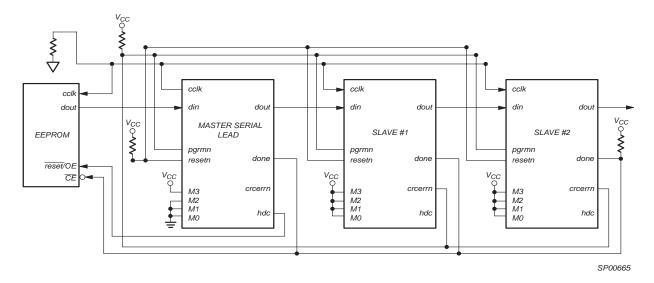

In Figure 17, the serial EEPROMs RESET/OE pin has been programmed to function with RESET active low and OE active high, and it is controlled by the XCR3320's hdc pin. This resets the serial EEPROMs during the initialization state and enables their output during the configuration state. If a bit error is found during configuration, hdc will go low, signifying the XCR3320 is back in initialization state and also resetting the EEPROMs. This restarts the configuration process.

The XCR3320 done pin is routed to the  $\overline{\text{CE}}$  pin of the EEPROMs. The Low signal on done during configuration enable the serial EEPROMs. At the completion of configuration, the High on done disables the EEPROMs.

In Figure 17, a serial EEPROM is programmed to configure a XCR3320. When configuration data requirements exceed the capacity of a single serial EEPROM, multiple serial EEPROMs can be cascaded to support the configuration of a single (or multiple) XCR3320(s). After the last bit from the first serial ROM is read, the serial ROM outputs  $\overline{\text{CEO}}$  Low and 3-states the DATA output. The next serial ROM recognizes the Low on  $\overline{\text{CE}}$  input and outputs configuration data on the DATA output. After configuration is complete, the XCR3320's done output into  $\overline{\text{CE}}$  disables the serial EEPROMs.

Figure 17: Master Serial Configuration

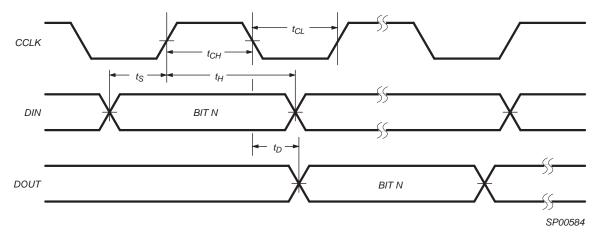

Figure 18: Master Serial Configuration Mode Timing Diagram

**Table 5: Master Serial Configuration Mode Timing Characteristics**

| Symbol          | Parameter               | Min. | Nom. | Max. | Unit |

|-----------------|-------------------------|------|------|------|------|

| $t_S$           | din setup time          | 60   | -    | -    | ns   |

| t <sub>H</sub>  | din hold time           | 0    | i    | -    | ns   |

| $t_D$           | cclk to dout delay      | -    | -    | 300  | ns   |

| $t_{CL}$        | cclk low time (M3 = 1)  | 357  | 500  | 833  | ns   |

| t <sub>CH</sub> | cclk high time (M3 = 1) | 357  | 500  | 833  | ns   |

| t <sub>C</sub>  | cclk frequency (M3 = 1) | 0.6  | 1.0  | 1.4  | MHz  |

In applications in which a serial EEPROM stores multiple configuration programs, the subsequent configuration program(s) are stored in EEPROM locations that follow the last address for the previous configuration program. The user must ensure that the serial EEPROMs address pointer is not reset, causing the first device configuration to be reloaded.

Contention on the XCR3320's din pin must be avoided. During configuration, din receives configuration data. After configuration, it is a user I/O.

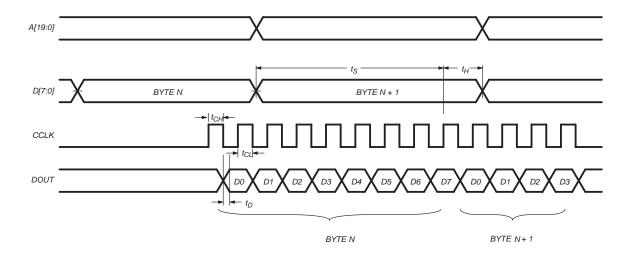

#### **Master Parallel Mode**

The master parallel configuration mode is generally used to interface to industry-standard byte-wide memory such as 256K and larger EEPROMs. Figure 19 provides the interface for master parallel mode. The XCR3320 outputs a 20-bit address on A[19:0] to memory and reads one byte of configuration data every eighth cclk. The parallel bytes are internally serialized starting with the least significant bit, D0. The starting memory address is 00000 Hex and the XCR3320 increments the address for each byte loaded. The starting address is output when the device enters the configuration state. The XCR3320 latches the data byte on the second rising edge of cclk. This next data byte is latched in the XCR3320 seven cclk cycles later.

SP00676 Figure 19: Master

Figure 20: Master Parallel Configuration Mode Timing Diagram

SP00585

Table 6: Master Parallel Configuration Mode Timing Characteristics

| Symbol          | Parameter                       | Min.   | Nom. | Max. | Unit |     |

|-----------------|---------------------------------|--------|------|------|------|-----|

| $t_{AV}$        | cclk to address valid           |        |      | -    | 200  | ns  |

| t <sub>S</sub>  | D[7:0] setup time to cclk high  |        |      |      | -    | ns  |

| t <sub>H</sub>  | D[7:0] hold time from cclk high |        |      |      | -    | ns  |

| t <sub>CL</sub> | cclk low time                   | M3 = 1 | 357  | 500  | 833  | ns  |

| t <sub>CH</sub> | cclk high time                  | M3 = 1 | 357  | 500  | 833  | ns  |

| t <sub>D</sub>  | cclk to dout delay              |        | -    |      | 300  | ns  |

| f <sub>C</sub>  | cclk frequency                  | M3 = 1 | 0.6  | 1.0  | 1.4  | MHz |

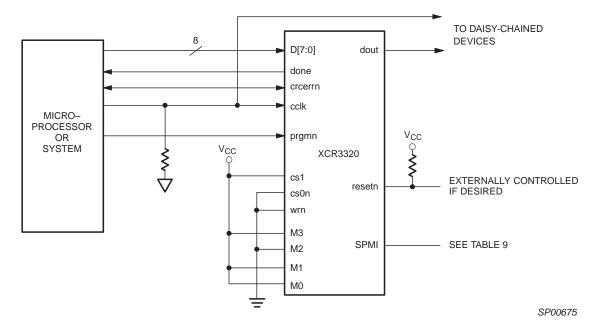

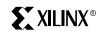

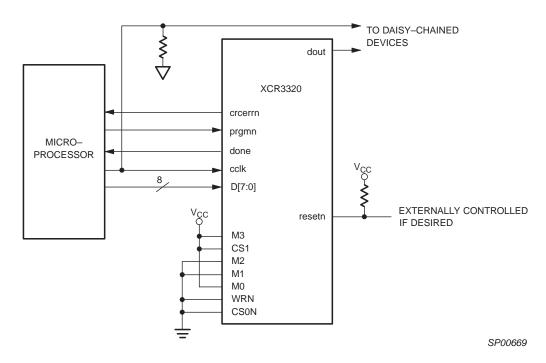

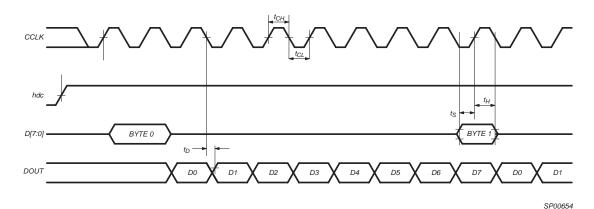

## Synchronous Peripheral Mode

In the synchronous peripheral mode, byte-wide data is input into D[7:0] on the rising edge of the cclk input. The first data byte is clocked in on the second cclk after hdc goes high. Subsequent data bytes are clocked in on every eighth rising edge of cclk. The process repeats until all of the data is loaded into the XCR3320. The serial data begins shifting out on dout 0.5 cycles after the parallel data was loaded. It requires additional cclks after the last byte is loaded to complete the shifting. Figure 21 shows the interface for synchronous peripheral mode. When configuring a single device, the frequency of cclk can be up to 10 MHz. As with master modes, this mode can be used for the lead

XCR3320 for daisy-chained devices. Note that the cclk frequency for daisy-chained operation is limited to 1 MHz.

Also note that CS1 is a multi-function pin, which means that it is available as a user I/O during normal device operation. As with all user I/O on the XCR3320, CS1 has an internal pull-down resistor that is automatically activated if the I/O pin is not used (see "Terminations" on page 8 for more information). If CS1 is left attached to  $V_{CC}$  after configuration, and it is not used as an I/O, the internal pull-down must be disabled or a path from  $V_{CC}$  to ground is created. To disable the pull-down, use the XPLA property statement 'signal name:pin number tri-state' to disable the resistor.

Figure 21: Synchronous Peripheral Configuration

Figure 22: Synchronous Peripheral Configuration Mode Timing Diagram

**Table 7: Synchronous Peripheral Configuration Mode Timing Characteristics**

| Symbol          | ı                 | Min.               | Max. | Unit |     |

|-----------------|-------------------|--------------------|------|------|-----|

| t <sub>S</sub>  | D[7:0] setup time |                    | 20   | 0    | ns  |

| t <sub>H</sub>  | D[7:0] hold time  |                    | 0    | -    | ns  |

| t <sub>CH</sub> | cclk high time    | Single device      | 50   | -    | ns  |

|                 |                   | Daisy-chain device | 500  | -    | ns  |

| t <sub>CL</sub> | cclk low time     | Single device      | 50   | -    | ns  |

|                 |                   | Daisy-chain device | 500  | -    | ns  |

| f <sub>C</sub>  | cclk frequency    | Single device      | -    | 10   | MHz |

|                 |                   | Daisy-chain device | -    | 1    | MHz |

#### **Slave Serial Mode**

Figure 23 shows the interface for the slave serial configuration mode. The configuration data is provided into the XCR3320's din input synchronous with the cclk input. After the XCR3320 has loaded its configuration data, it re-transmits incoming configuration data on dout. When configuring a single device, the frequency of cclk can be up to 10 MHz.

A device in slave serial mode can be used as the lead device in a daisy-chain. When used in daisy-chained oper-

ation, cclk is routed into all slave serial mode devices in parallel and the frequency is limited to 1 MHz. The dout pin of the lead device is connected to the din pin of the next device and so on. In daisy-chained operation, all downstream devices use slave serial mode regardless of the configuration mode of the lead device.

Multiple slave XCR3320s can be loaded with identical configurations simultaneously. This is done by loading the configuration data into the din inputs in parallel.

Figure 23: Slave Serial Configuration Schematic

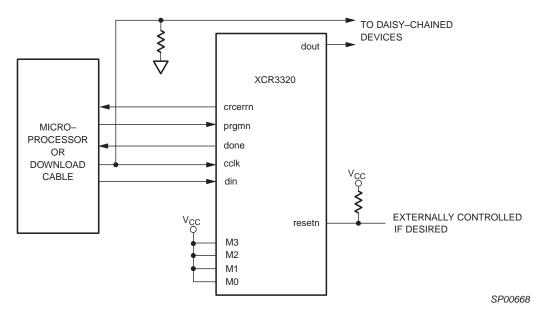

Figure 24: Slave Serial Configuration Mode Timing Diagram

Table 8: Slave Serial Configuration Mode Timing Characteristics

| Symbol          |                | Min                | Max. | Unit |     |

|-----------------|----------------|--------------------|------|------|-----|

| t <sub>S</sub>  | din setup time | 20                 | 0    | ns   |     |

| t <sub>H</sub>  | din hold time  |                    | 0    | -    | ns  |

| t <sub>CH</sub> | cclk high time | Single device      | 50   | -    | ns  |

|                 |                | Daisy-chain device | 500  | -    | ns  |

| t <sub>CL</sub> | cclk low time  | Single device      | 50   | -    | ns  |

|                 |                | Daisy-chain device | 500  | -    | ns  |

| f <sub>C</sub>  | cclk frequency | Single device      | -    | 10   | MHz |

|                 |                | Daisy-chain device | -    | 1    | MHz |

## **Slave Parallel Mode**

The slave parallel mode is essentially the same as the synchronous peripheral mode, except that the chip select pins (cs1 and cs0n) are not used. As in the synchronous peripheral mode, byte-wide data is input into D[7:0] on the rising edge of the cclk input. The first data byte is clocked in on the second cclk after hdc goes High. Subsequent data bytes are clocked in on every eighth rising edge of cclk. The process repeats until all of the data is loaded into the XCR3320. The serial data begins shifting out on dout 0.5

cycles after the parallel data was loaded. It requires additional cclks after the last byte is loaded to complete the shifting. Figure 25 shows the interface for slave parallel mode. When configuring a single device, the frequency of cclk can be up to 10 MHz.

As with synchronous peripheral mode, the slave parallel mode can be used as the lead XCR3320 for daisy-chained devices. Note that the cclk frequency for daisy-chain operation is limited to 1 MHz.

Figure 25: Slave Parallel Configuration Schematic

Figure 26: Slave Parallel Configuration Mode Timing Diagram

**Table 9: Slave Parallel Configuration Mode Timing Characteristics**

| Symbol          |                   | Min.               | Max. | Unit |     |

|-----------------|-------------------|--------------------|------|------|-----|

| t <sub>S</sub>  | D[7:0] setup time |                    | 20   | 0    | ns  |

| t <sub>H</sub>  | D[7:0] hold time  |                    | 0    | -    | ns  |

| t <sub>CH</sub> | cclk high time    | Single device      | 50   | -    | ns  |

|                 |                   | Daisy-chain device | 500  | -    | ns  |

| t <sub>CL</sub> | cclk low time     | Single device      | 50   | -    | ns  |

|                 |                   | Daisy-chain device | 500  | -    | ns  |

| f <sub>C</sub>  | cclk frequency    | Single device      | -    | 10   | MHz |

|                 |                   | Daisy-chain device | -    | 1    | MHz |

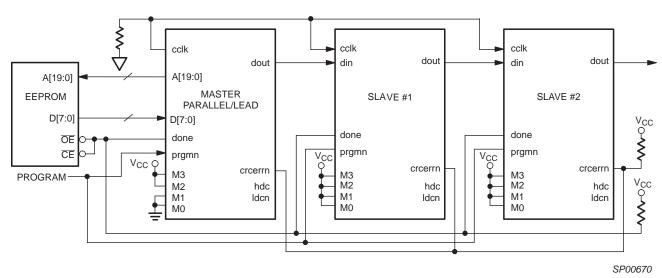

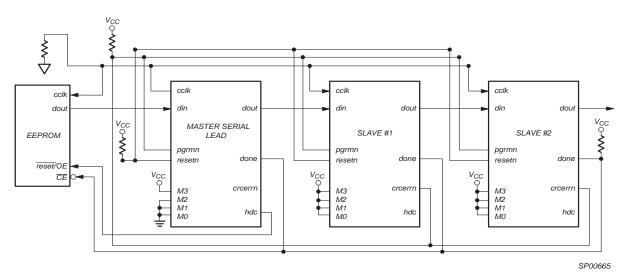

# **Daisy Chain Operation**

Multiple XCR3320s can be configured by using a daisy-chain of XCR3320s. Daisy-chaining uses a lead XCR3320 and one or more XCR3320s configured in slave serial mode. The lead XCR3320 can be configured in any mode. Figure 27 shows the connections for loading multiple XCR3320s in a daisy-chain configuration with the lead devices configured in master parallel mode. Figure 28 shows the connections for loading multiple XCR3320's with the lead device configured in master serial mode.

Daisy-chained XCR3320s are connected in series. An upstream XCR3320 which has received the preamble outputs a high on dout, ensuring that downstream XCR3320s do not receive frame start bits. When the lead device receives the postamble, its configuration is complete. At this point, the configuration RAM of the lead device is full and its done pin is released. The lead device continues to load configuration data until the internal frame bit counter reaches the length count or all the done pins of the chain have gone high. Since the configuration RAM of the lead device is full, this data is shifted out serially to the downstream devices on the dout pin. As the configuration is completed for the downstream devices, each will release its done pin. Because the done pins of each device in the chain are wire-anded together, the done pin will be pulled

high when all devices in the daisy-chain have completed configuration. All devices now move to the start-up state simultaneously.

The generation of cclk for the daisy-chained devices which are in slave serial mode differs depending on the configuration mode of the lead device. A master parallel mode device uses its internal timing generator to produce an internal cclk. If the lead device is configured in either synchronous peripheral, slave serial mode, or slave parallel mode, cclk is an input and is mated to the lead device and to all of the daisy-chained devices in parallel. The configuration data is read into din of slave devices on the positive edge of cclk, and shifted out dout on the negative edge of cclk. Note that daisy-chain operation is limited to a cclk frequency of 1 MHz. If a CRC error or an invalid preamble is detected by a slave device, crcerrn will be pulled low and in turn pull prgmn low, halting configuration for all devices. If a CRC error is detected by the master device, hdc will be pulled low, resetting the EEPROM to the first address and restarting configuration.

The development software can create a composite configuration file for configuring daisy-chained XCR3320s. The configuration data consists of multiple concatenated data packets.

Figure 27: Daisy-Chain Schematic with Lead Device in Master Parallel

Figure 28: Daisy Chain Schematic with Master Serial Lead Device

## **JTAG Testing Capability**

JTAG is the commonly-used acronym for the Boundary Scan Test (BST) feature defined for integrated circuits by IEEE Standard 1149.1. This standard defines input/output pins, logic control functions, and commands which facilitate both board and device level testing without the use of specialized test equipment. BST provides the ability to test the external connections of a device, test the internal logic of the device, and capture data from the device during normal operation. BST provides a number of benefits in each of the following areas:

- Testability

- Allows testing of an unlimited number of interconnects on the printed circuit board

- Testability is designed in at the component level

- Enables desired signal levels to be set at specific pins (Preload)

- Data from pin or core logic signals can be examined during normal operation

- Reliability

- Eliminates physical contacts common to existing test fixtures (e.g., "bed-of-nails")

- Degradation of test equipment is no longer a concern

- Facilitates the handling of smaller, surface-mount components

- Allows for testing when components exist on both sides of the printed circuit board

- Cost

- Reduces/eliminates the need for expensive test equipment

- Reduces test preparation time

- Reduces spare board inventories

The Xilinx XCR3320's JTAG interface includes a TAP Port and a TAP Controller, both of which are defined by the IEEE 1149.1 JTAG Specification. As implemented in the Xilinx XCR3320, the TAP Port includes five pins (refer to Table 10) described in the JTAG specification:  $t_{\text{CK}},\,t_{\text{MS}},\,t_{\text{DI}},\,t_{\text{DO}},$  and  $t_{\text{RSTN}}.$  These pins should be connected to an external pull-up resistor to keep the JTAG signals from floating when they are not being used.

Table 11 defines the dedicated pins used by the mandatory JTAG signals for the XCR3320.

The JTAG specifications define two sets of commands to support boundary-scan testing: high-level commands and low-level commands. High-level commands are executed via board test software on an a user test station such as automated test equipment, a PC, or an engineering work-station (EWS). Each high-level command comprises a sequence of low level commands. These low-level commands are executed within the component under test, and therefore must be implemented as part of the TAP Controller design. The set of low-level boundary-scan commands implemented in the XCR3320 is defined in Table 11. By supporting this set of low-level commands, the XCR3320 allows execution of all high-level boundary-scan commands.

**Table 10: JTAG Pin Description**

| Pin   | Name              | Description                                                                                                                                                                |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tck   | Test Clock Output | Clock pin to shift the serial data and instructions in and out of the tdi and tdo pins, respectively. tck is also used to clock the TAP Controller state machine.          |

| tms   | Test Mode Select  | Serial input pin selects the JTAG instruction mode. tms should be driven high during user mode operation.                                                                  |

| tdi   | Test Data Input   | Serial input pin for instructions and test data. Data is shifted in on the rising edge of tck.                                                                             |

| tdo   | Test Data Output  | Serial output pin for instructions and test data. Data is shifted out on the falling edge of tck. The signal is tri-stated if data is not being shifted out of the device. |

| trstn | Test Reset        | Forces TAP controller to test logic reset state. This signal is active low.                                                                                                |

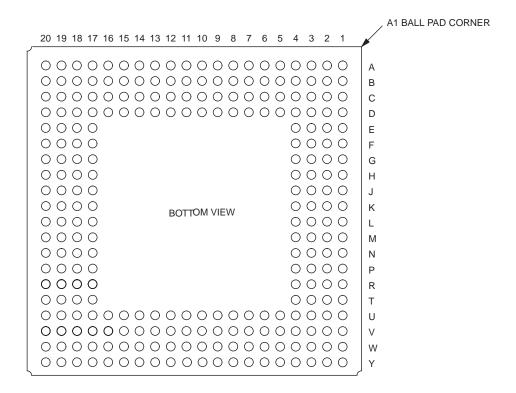

Table 11: XCR3320 JTAG Pinout by Package Type

| Device: XCR3320 | (Pin Number / Macrocell #) |                 |                 |                 |                   |  |  |

|-----------------|----------------------------|-----------------|-----------------|-----------------|-------------------|--|--|

| Device. ACR3320 | t <sub>CK</sub>            | t <sub>MS</sub> | t <sub>DL</sub> | t <sub>DO</sub> | t <sub>RSTN</sub> |  |  |

| 256-pin PBGA    | V4                         | W4              | U5              | Y4              | L18               |  |  |

| 160-pin LQFP    | 41                         | 43              | 42              | 44              | 97                |  |  |

Table 12: XCR3320 Low-Level JTAG Boundary-Scan Commands

| Instruction<br>(Instruction Code)<br>Register Used  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD<br>(00010)<br>Boundary-Scan Register | The mandatory SAMPLE/PRELOAD instruction allows a snapshot of the normal operation of the component to be taken and examined. It also allows data values to be loaded onto the latched parallel outputs of the Boundary-Scan Shift-Register prior to selection of the other boundary-scan test instructions.                                                                                                                                                                                                                                                                                     |

| EXTEST<br>(00000)<br>Boundary-Scan Register         | The mandatory EXTEST instruction allows testing of off-chip circuitry and board level interconnections. Data would typically be loaded onto the latched parallel outputs of Boundary-Scan Shift-Register using the SAMPLE/PRELOAD instruction prior to selection of the EXTEST instruction.                                                                                                                                                                                                                                                                                                      |

| BYPASS<br>(11111)<br>Bypass Register                | Places the 1-bit bypass register between the tdi and tdo pins, which allows the BST data to pass synchronously through the selected device to adjacent devices during normal device operation. The BYPASS instruction can be entered by holding tdi at a constant high value and completing an Instruction-Scan cycle.                                                                                                                                                                                                                                                                           |

| IDCODE<br>(00001)<br>Boundary-Scan Register         | Selects the IDCODE register and places it between tdi and tdo, allowing the IDCODE to be serially shifted out of tdo. The IDCODE instruction permits blind interrogation of the components assembled onto a printed circuit board. Thus, in circumstances where the component population may vary, it is possible to determine what components exist in a product.                                                                                                                                                                                                                               |

| HIGHZ<br>(00101)<br>Bypass Register                 | The HIGHZ instruction places the component in a state in which <u>all</u> of its system logic outputs are placed in an inactive drive state (e.g., high impedance). In this state, an in-circuit test system may drive signals onto the connections normally driven by a component output without incurring the risk of damage to the component. The HIGHZ instruction also forces the Bypass Register between tDI and tDO.                                                                                                                                                                      |

| INTEST<br>(00011)<br>Boundary-Scan Register         | The INTEST instruction allows testing of the on-chip system logic while the component is assembled on the board. The boundary-scan register is connected between TDI and TDO. Using the INTEST instruction, test stimuli are shifted in one at a time and applied to the on-chip system logic. The test results are captured into the boundary-scan register and are examined by subsequent shifting, Data would typically be loaded onto the latched parallel outputs of boundary-scan shift-register stages using the SAMPLE/PRELOAD instruction prior to selection of the INTEST instruction. |

|                                                     | NOTE: Following use of the INTEST instruction, the on-chip system logic may be in an indeterminate state that will persist until a system reset is applied. Therefore, the on-chip system logic may need to be reset on return or normal (i.e., non-test) operation.                                                                                                                                                                                                                                                                                                                             |

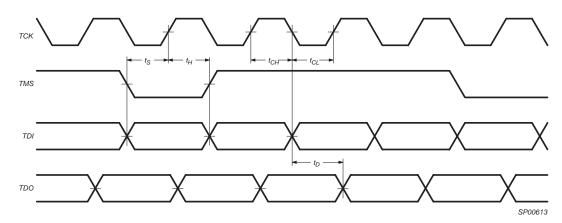

Figure 29: Boundary Scan Timing Diagram

**Table 13: Boundary Scan Timing Characteristics**

| Symbol           | Parameter                  | Min | Max. | Unit |

|------------------|----------------------------|-----|------|------|

| t <sub>S</sub>   | tdi/tms to tck setup time  | 20  | -    | ns   |

| t <sub>H</sub>   | tdi/tms from tck hold time | 0   | -    | ns   |

| t <sub>CH</sub>  | tck high time              | 50  | -    | ns   |

| t <sub>CL</sub>  | tck low time               | 50  | -    | ns   |

| f <sub>TCK</sub> | tck frequency              | -   | 10   | MHz  |

| t <sub>D</sub>   | tck to tdo delay           | -   | 35   | ns   |

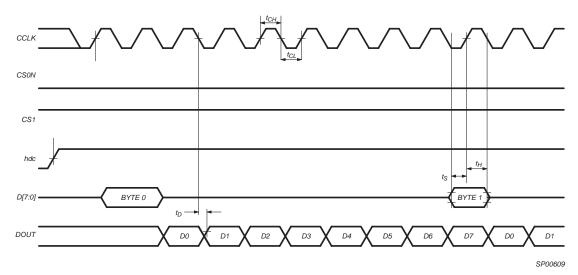

# **Device Configuration Through JTAG**

In addition to the normal configuration modes, the XCR3320 can also be configured through the JTAG port. This feature is very useful for design prototyping and debug before the device is put into the final product. In System Configuration of the XCR3320 is supported by Xilinx

PC-ISP software. Table 14 shows the ISC commands supported by the XCR3320

To configure the device through the JTAG port, mode pins M0, M1, and M2 should all be held low. M3, as always, should be high and the JTAG pins should be terminated as described in "Terminations" on page 8 of this data sheet.

Table 14: Low Level ISP Commands

| Instruction (Register Used)     | Instruction<br>Code | Description                                                                                                                                                                                                                             |

|---------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable<br>(ISP Shift Register)  | 1001                | Enables the Erase, Program, and Verify commands. Using the ENABLE instruction before the Erase, Program, and Verify instructions allows the user to specify the outputs the device using the JTAG Boundary-Scan SAMPLE/PRELOAD command. |

| Erase<br>(ISP Shift Register)   | 1010                | Erases the entire EEPROM array. The outputs during this operation can be defined by user by using the JTAG SAMPLE/PRELOAD command.                                                                                                      |

| Program<br>(ISP Shift Register) | 1011                | Programs the data in the ISP Shift Register into the addressed EEPROM row. The outputs during this operation can be defined by user by using the JTAG SAMPLE/PRELOAD command.                                                           |

| Verify<br>(ISP Shift Register)  | 1100                | Transfers the data from the addressed row to the ISP Shift Register. The data can then be shifted out and compared with the JEDEC file. The outputs during this operation can be defined by the user.                                   |

# **Absolute Maximum Ratings<sup>1</sup>**

| Symbol           | Parameter                  | Min  | Max.                 | Unit |

|------------------|----------------------------|------|----------------------|------|

| $V_{CC}$         | Supply voltage             | -0.5 | 4.6                  | V    |

| $V_{IN}$         | Input voltage              | -1.2 | 5.75                 | V    |

| V <sub>OUT</sub> | Output voltage             | -0.5 | V <sub>CC</sub> +0.5 | V    |

| I <sub>IN</sub>  | Input current              | -30  | 30                   | mA   |

| $T_J$            | Junction temperature range | -40  | 150                  | °C   |

| T <sub>STG</sub> | Storage temperature range  | -65  | 150                  | °C   |

#### Note:

# **Operating Range**

| Product Grade | Temperature | Voltage   |

|---------------|-------------|-----------|

| Commercial    | 0 to 70°C   | 3.3V ±10% |

| Industrial    | -40 to 85°C | 3.3V ±10% |

# **DC Electrical Characteristics For Commercial Grade Devices**

Commercial temperature range:  $V_{CC}$  = 3.0V to 3.6V;  $0^{\circ}C < T_{AMB} < 70^{\circ}C$

| Symbol            | Parameter                     | Test Conditions                                                                        | Min. | Max. | Unit |

|-------------------|-------------------------------|----------------------------------------------------------------------------------------|------|------|------|

| $V_{IH}$          | Input high voltage            |                                                                                        | 2.0  | 5.5  | ٧    |

| V <sub>IL</sub>   | Input low voltage             |                                                                                        | -0.3 | 0.8  | V    |

| V <sub>OH</sub>   | Output high voltage           | I <sub>OH</sub> = -8 mA                                                                | 2.4  | -    | V    |

| V <sub>OL</sub>   | Output low voltage            | I <sub>OL</sub> = 8 mA                                                                 | -    | 0.4  | V    |

| I <sub>I</sub>    | Input leakage current         | V <sub>I</sub> = 0 or 5.5V                                                             | -10  | 10   | μΑ   |

| I <sub>CCSB</sub> | Standby current               | T <sub>AMB</sub> = 25°C; no output loads, inputsatV <sub>CC</sub> or V <sub>SS</sub> . | -    | 100  | μΑ   |

| C <sub>IN</sub>   | Input capacitance             | $T_{AMB} = 25$ °C; $V_{CC} = 3.3V$ ; $f = 1 \text{ MHz}$                               | -    | 10   | pF   |

| C <sub>IO</sub>   | I/O capacitance               | $T_{AMB} = 25$ °C; $V_{CC} = 3.3V$ ; $f = 1 \text{ MHz}$                               | -    | 10   | pF   |

| C <sub>CLK</sub>  | Clock pin capacitance         | $T_{AMB} = 25$ °C; $V_{CC} = 3.3V$ ; $f = 1 \text{ MHz}$                               | -    | 12   | pF   |

| R <sub>DONE</sub> | done pull-up resistor         | $V_{CC} = 3.0V; V_{IN} = 0V$                                                           | 5    | 20   | kΩ   |

| R <sub>PD</sub>   | Unused I/O pull-down resistor | $V_{CC} = 3.6V; V_{IN} = V_{CC}$                                                       | 100  | 400  | kΩ   |

| I <sub>OZH</sub>  | Input leakage                 | V <sub>IN</sub> = 5.5V or 3.6V                                                         | -10  | 10   | μΑ   |

| I <sub>OZL</sub>  | Input leakage                 | $V_{IN} = 0V$                                                                          | -10  | 10   | μΑ   |

Stresses above these listed may cause malfunction or permanent damage to the device. This is a stress rating only.

Functional operation at these or any other condition above those indicated in the operational and programming specification is not implied.

# **AC Electrical Characteristics For Commercial Grade Devices**

Commercial temperature range:  $V_{CC}$  = 3.0V to 3.6V;  $0^{\circ}C$  <  $T_{AMB}$  <  $70^{\circ}C$

| Symbol               | Parameter                                                                 | (    | C7   |      | :10  | Unit |

|----------------------|---------------------------------------------------------------------------|------|------|------|------|------|

|                      |                                                                           | Min. | Max. | Min. | Max. |      |

| Timing Re            | quirements                                                                |      |      |      |      |      |

| t <sub>CL</sub>      | Clock LOW time                                                            | 2.5  |      | 3.0  |      | ns   |

| t <sub>CH</sub>      | Clock HIGH time                                                           | 2.5  |      | 3.0  |      | ns   |

| t <sub>SU_PAL</sub>  | PAL setup time (Global clock)                                             | 3.0  |      | 4.0  |      | ns   |

| t <sub>SU_PLA</sub>  | PLA setup time (Global clock)                                             | 4.5  |      | 5.5  |      | ns   |

| t <sub>SU_XOR</sub>  | XOR setup time (Global clock)                                             | 5.5  |      | 6.5  |      | ns   |

| t <sub>H</sub>       | Hold time (Global clock)                                                  |      | 0    |      | 0    | ns   |

| Output Ch            | aracteristics                                                             |      |      |      |      |      |

| t <sub>PD_PAL</sub>  | Input to output delay through PAL                                         |      | 7.5  |      | 10.0 | ns   |

| t <sub>PD_PLA</sub>  | Input to output delay through PLA                                         |      | 9.0  |      | 11.5 | ns   |

| t <sub>PD_XOR</sub>  | Input to output delay through XOR                                         |      | 10.0 |      | 12.5 | ns   |

| t <sub>PDF_PAL</sub> | Input (or feedback node) to internal feedback node delay time through PAL |      | 4.5  |      | 6.0  | ns   |

| t <sub>PDF_PLA</sub> | Input (or feedback node) to internal feedback node delay time through PLA |      | 6.0  |      | 7.5  | ns   |

| t <sub>PDF_XOR</sub> | Input (or feedback node) to internal feedback node delay time through XOR |      | 7.0  |      | 8.5  | ns   |

| t <sub>CF</sub>      | Global clock to feedback delay                                            |      | 3.0  |      | 3.5  | ns   |

| t <sub>CO</sub>      | Global clock to out delay                                                 |      | 6.0  |      | 7.5  | ns   |

| t <sub>CS</sub>      | Clock skew (variance for switching outputs with common global clock)      |      | 1.0  |      | 1.5  | ns   |

| f <sub>MAX1</sub>    | Maximum flip-flop toggle rate:                                            | 200  |      | 166  |      | MHz  |

|                      | $\left(\frac{1}{t_{CL}+t_{CH}}\right)$                                    |      |      |      |      |      |

| f <sub>MAX2</sub>    | Maximum internal frequency: $\left(\frac{1}{t_{SU-PAL}+t_{CF}}\right)$    | 166  |      | 133  |      | MHz  |

| f <sub>MAX3</sub>    | Maximum external frequency: $\left(\frac{1}{t_{SU-PAL}+t_{CO}}\right)$    | 111  |      | 87   |      | MHz  |

| t <sub>BUFF</sub>    | Output buffer delay (fast)                                                |      | 3.0  |      | 4.0  | ns   |

| t <sub>SSR</sub>     | Slow slew rate incremental delay                                          |      | 5.0  |      | 6.0  | ns   |

| $t_{EA}$             | Output enable delay                                                       |      | 10.0 |      | 12.0 | ns   |

| t <sub>ER</sub>      | Output disable delay <sup>1</sup>                                         |      | 10.0 |      | 12.0 | ns   |

| t <sub>GTSA</sub>    | Global 3-state enable                                                     |      | 10.0 |      | 12.0 | ns   |

| t <sub>GTSR</sub>    | Global 3-state disable                                                    |      | 10.0 |      | 12.0 | ns   |

| t <sub>RR</sub>      | Input to register reset                                                   |      | 10.5 |      | 12.0 | ns   |

| t <sub>RP</sub>      | Input to register preset                                                  |      | 9.5  |      | 11.0 | ns   |

| t <sub>GRR</sub>     | Global reset to register reset                                            |      | 10   |      | 12.0 | ns   |

| t <sub>GZIA</sub>    | Global ZIA delay                                                          |      | 2.0  |      | 2.5  | ns   |

Note:

1. Output  $C_L = 5.0 pF$ .

# **DC Electrical Characteristics For Industrial Grade Devices**

Industrial temperature range:  $V_{CC}$  = 3.0V to 3.6V; -40°C <  $T_{AMB}$  < 85°C

| Symbol            | Parameter                     | Test Conditions                                                      | Min. | Max. | Unit |

|-------------------|-------------------------------|----------------------------------------------------------------------|------|------|------|

| $V_{IH}$          | Input high voltage            |                                                                      | 2.0  | 5.5  | V    |

| V <sub>IL</sub>   | Input low voltage             |                                                                      | -0.3 | 0.8  | V    |

| V <sub>OH</sub>   | Output high voltage           | I <sub>OH</sub> = -8 mA                                              | 2.4  | -    | V    |

| $V_{OL}$          | Output low voltage            | I <sub>OL</sub> = 8 mA                                               | -    | 0.4  | V    |

| I <sub>I</sub>    | Input leakage current         | V <sub>I</sub> = 0 or 5.5V                                           | -10  | 10   | μΑ   |

| I <sub>CCSB</sub> | Standby current               | $T_{amb} = 25$ °C; no output loads, inputs at $V_{CC}$ or $V_{SS}$ . | -    | 100  | μΑ   |

| C <sub>IN</sub>   | Input capacitance             | $T_{AMB} = 25^{\circ}C; V_{CC} = 3.3V; f = 1 MHz$                    | -    | 10   | pF   |

| C <sub>IO</sub>   | I/O capacitance               | $T_{AMB} = 25^{\circ}C; V_{CC} = 3.3V; f = 1 MHz$                    | -    | 10   | pF   |

| C <sub>CLK</sub>  | Clock pin capacitance         | $T_{AMB} = 25^{\circ}C; V_{CC} = 3.3V; f = 1 MHz$                    | -    | 12   | pF   |

| R <sub>DONE</sub> | done pull-up resistor         | $V_{CC} = 3.0V; V_{IN} = 0V$                                         | 5    | 20   | kΩ   |

| R <sub>PD</sub>   | Unused I/O pull-down resistor | $V_{CC} = 3.6V$ ; $V_{IN} = V_{CC}$                                  | 100  | 400  | kΩ   |

| I <sub>OZH</sub>  | Input leakage                 | V <sub>IN</sub> = 5.5V or 3.6V                                       | -10  | 10   | μΑ   |

| I <sub>OZL</sub>  | Input leakage                 | V <sub>IN</sub> = 0.0 V                                              | -10  | 10   | μΑ   |

# **AC Electrical Characteristics For Industrial Grade Devices**

Industrial temperature range:  $V_{CC}$  = 3.0V to 3.6V; -40°C <  $T_{AMB}$  < 85°C

|                      | ъ .                                                | N    |      |        |

|----------------------|----------------------------------------------------|------|------|--------|

| Symbol               | Parameter                                          | Min. | Max. | - Unit |

| Timing Requ          | irements                                           |      |      |        |

| CL                   | Clock LOW time                                     | 2.5  |      | ns     |

| CH                   | Clock HIGH time                                    | 2.5  |      | ns     |

| SU_PAL               | PAL setup time (Global clock)                      | 3.5  |      | ns     |

| SU_PLA               | PLA setup time (Global clock)                      | 5.0  |      | ns     |

| SU_XOR               | XOR setup time (Global clock)                      | 6.0  |      | ns     |

| H                    | Hold time (Global clock)                           |      | 0    | ns     |

| Output Chara         | acteristics                                        |      |      | •      |

| PD_PAL               | Input to output delay through PAL                  |      | 8.5  | ns     |

| PD_PLA               | Input to output delay through PLA                  |      | 10   | ns     |

| PD_XOR               | Input to output delay through XOR                  |      | 11   | ns     |

| PDF_PAL              | Input (or feedback node) to internal feedback node |      | 5.0  | ns     |

| _                    | delay time through PAL                             |      |      |        |

| t <sub>PDF_PLA</sub> | Input (or feedback node) to internal feedback node |      | 6.5  | ns     |

|                      | delay time through PLA                             |      |      |        |

| t <sub>PDF_XOR</sub> | Input (or feedback node) to internal feedback node |      | 7.5  | ns     |

|                      | delay time through XOR                             |      |      |        |

| CF                   | Global clock to feedback delay                     |      | 3.5  | ns     |

| co                   | Global clock to out delay                          |      | 7.0  | ns     |

| cs                   | Clock skew (variance for switching outputs with    |      | 1.0  | ns     |

| ,                    | common global clock)                               | 200  |      | NAL I  |

| MAX1                 | Maximum flip-flop toggle rate:                     | 200  |      | MHz    |

|                      | $\left(\frac{1}{t_{CL}+t_{CH}}\right)$             |      |      |        |

| MAX2                 | Maximum internal frequency:                        | 143  |      | MHz    |

|                      | $\left(\frac{1}{t_{SU-PAL}+t_{CF}}\right)$         |      |      |        |

| f <sub>MAX3</sub>    | Maximum external frequency:                        | 95   |      | MHz    |